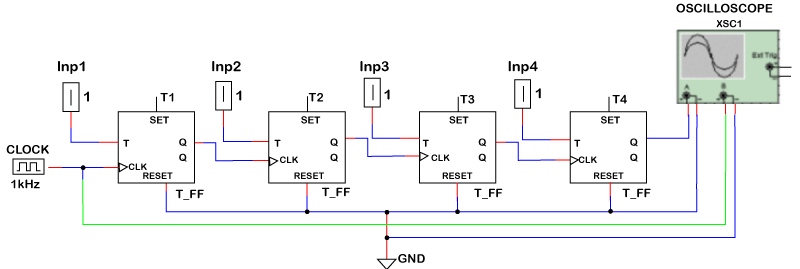

Verilog Ripple CounterA ripple counter is an asynchronous counter in which the preceding flop's output clocks all the flops except the first. Asynchronous means all the elements of the circuits do not have a common clock. For example, a 4 bit counter will count from 0000 to 1111. DesignWe will supply a 1Khz clock signal to the first T Flip Flop, and the rest of the three Flip Flops will have their clocks from the output (Q) of the previous Flip Flop. See the schematic below:

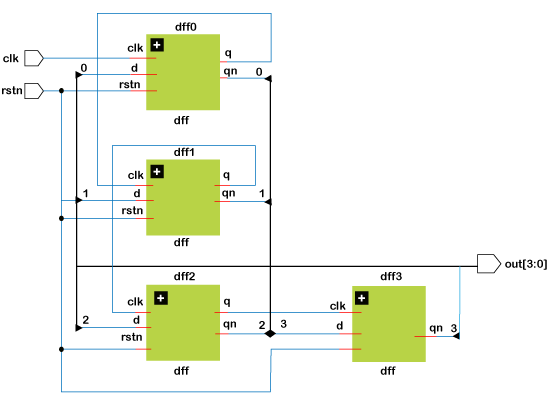

The above circuit contains 4 T Flip Flops because we need 4 bit Ripple Counter. T1 has its clock supplied by a Digital source of 1Khz, and the rest of Flip Flops used previous Flip Flop output as the clock. Input T of all T flip flops is HIGH (1) so that T Flip Flop toggles input on every clock edge. ExampleWe will do three modules to implement this counter. The first module is to implement the main program. The second module is used to implement T flip flop logic and the third to implement D Flip Flop logic. Hardware Schematic

Testbench

Next TopicVerilog Ring Counter

|

For Videos Join Our Youtube Channel: Join Now

For Videos Join Our Youtube Channel: Join Now

Feedback

- Send your Feedback to [email protected]

Help Others, Please Share