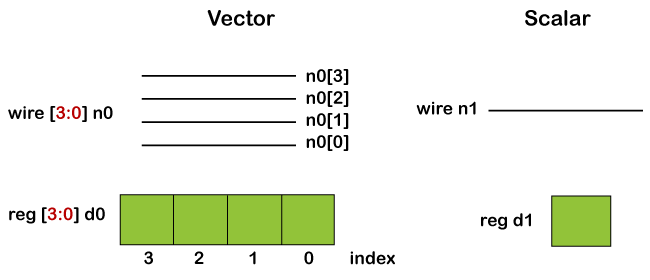

Verilog Scalar and VectorVerilog needs to represent individual bits as well as groups of bits. A single bit sequential element is a flip-flop, and a 16-bit sequential element is a register. For these kinds of tasks, Verilog has scalar and vector. Scalar and VectorA net or reg declaration without a range specification is considered 1 bit wide and is a scalar. If a range is specified, the net or reg becomes a multibit entity known as a vector.

Vector range specification contains two constant expressions such as:

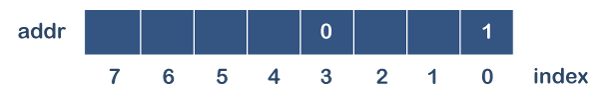

A colon should separate the MSB and LSB constant expressions. The MSB constant expression and the LSB constant expression can be any value from positive, negative, and zero. The LSB constant expression can be higher, equal, or less than the MSB constant expression. Both the MSB and the LSB expressions should be constant expressions. Vectors can be declared for all types of net data types and reg data types. Specifying vectors for integer, real, realtime, and time data types is illegal. Vector nets and registers are treated as unsigned values. Syntax The following is the simplified syntax of the vectors, such as: Examples The range gives the ability to address individual bits in a vector. The most significant bit of the vector should be specified as the left-hand value in the range. While the least significant bit of the vector should be specified on the right. The MSB and LSB should be a constant expression and cannot be substituted by a variable. But they can be any integer value such as positive, negative, or zero. The LSB value can be higher than, less than, or equal to the MSB value. Bit SelectsAny bit in a vectored variable can be individually selected and assigned a new value, as shown in the below image. This is called a bit select.

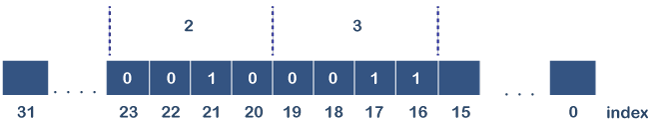

If the bit select is out of bounds or the bit select is x or z, then the value returned will be x. Part SelectsThe selection of the range of contiguous bits is called the part selected. There are two types of part selects.

A variable part select allows it to be used effectively in loops to select parts of the vector. Although the starting bit can be varied, the width has to be constant. Syntax Example

Next TopicVerilog Arrays

|

For Videos Join Our Youtube Channel: Join Now

For Videos Join Our Youtube Channel: Join Now

Feedback

- Send your Feedback to [email protected]

Help Others, Please Share